Introdução a Flip-Flop

Henrique Almeida Louzada

Você vai aprender

Circuito lógico de um Flip-Flop

Tipos de Flip-Flop

Exemplo de uso de um Flip-Flop

pré-requisitos

Conhecimento básico de Circuitos Lógicos

flip-flop

Flip-flop (ou multivibrador biestável) é um circuito digital pulsado capaz de servir como uma memória de um bit. Um flip-flop tipicamente inclui zero, um ou dois sinais de entrada, um sinal de clock, e um sinal de saída dividido em Q e Q', onde Q' é sempre o valor de Q inverso. Alguns flip-flops também incluem um sinal da entrada clear, que limpa a saída atual. A pulsação (mudança no sinal do clock) faz com que o flip-flop mude ou retenha seu sinal de saída, baseado nos valores dos sinais de entrada e na equação característica do flip-flop.

De forma geral os flip-flops tem dois estados de saída, para o flip-flop assumir um destes estados é necessário que haja uma combinação das variáveis e do clock. Após este pulso, o flip-flop permanecerá neste estado até a chegada de um novo pulso de clock e, então, de acordo com as variáveis de entrada, mudará ou não de estado.

Veremos abaixo mais sobre flip-flops específicos e seus circuitos:

flip-flop toggle

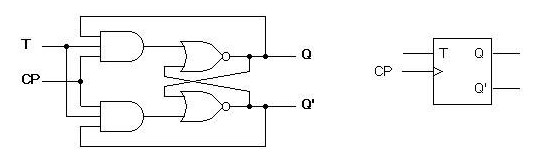

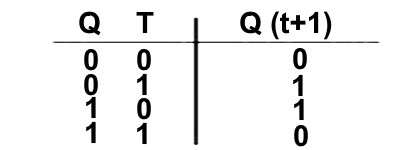

Circuito de um flip-flop do tipo Toggle

Tabela verdade de um flip-flop do tipo Toggle

O flip-flop tipo Toggle só executa duas funções: Memorizar e Trocar. Como a principal função é a de Troca, é chamado então de flip-flop tipo T, de Troca ou Toggle. Pode ser implementado independentemente, mas geralmente é implementado por um flip-flop JK, como veremos mais abaixo.

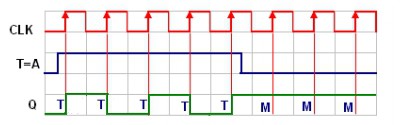

Aqui há um exemplo de análise do comportamento das saídas de acordo as entradas, com T = 0 (mantém Q) e com T = 1 (modo Toggle):

Obs.: Ignoramos o atraso no tempo de subida e tempo de descida da onda de clock, isso poderá ser visto em um estudo mais aprofundado de flip-flops. Trabalharemos apenas com ambiente ideal, clock muda de nível baixo para alto instantaneamente e vice e versa.

flip-flops sr (set e reset)

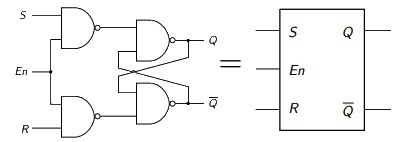

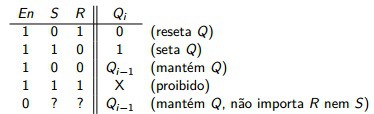

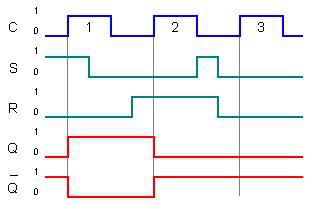

Circuito de um flip-flop do tipo SR

Tabela verdade de um flip-flop do tipo SR

Um flip-flop SR é um biestável básico, dele se derivam os demais tipos. O flip-flop SR ativa (set, muda sua saída para o nível lógico 1, ou retém se este já estiver em 1) se a entrada S (set) estiver em 1 e a entrada R (reset) estiver em 0 quando o clock for mudado. O flip-flop desativa (reset, muda sua saída para o nível lógico 0, ou a mantém se esta já estiver em 0) se a entrada R (reset) estiver em 1 e a entrada S (set) estiver em 0 quando o clock estiver habilitado. Se ambas as entradas estiverem em 0 quando o clock for mudado, a saída não se modifica. Entretanto, se ambas as entradas estiverem em 1 quando o clock estiver habilitado, nenhum comportamento particular é garantido.

Podemos ver abaixo um exemplo de análise do comportamento das saídas de acordo as entradas em três tempos de clock:

Considere nível alto como '1' e nível baixo como '0'

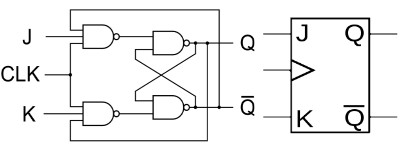

flip-flop jk

Circuito Lógico de um flip-flop do tipo JK

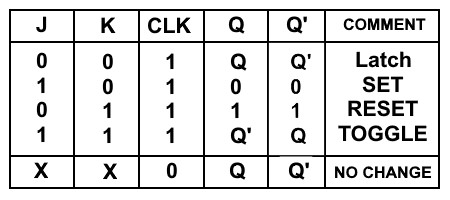

Tabela verdade de um flip-flop do tipo JK, onde seta para cima significa clock no nível alto.

Onde Q' = Q

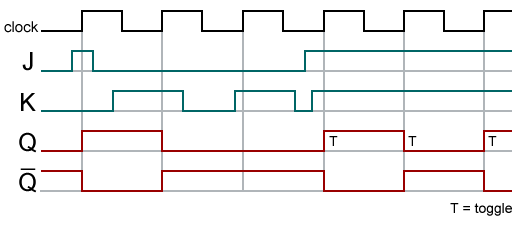

O flip-flop JK aprimora o funcionamento do flip-flop RS interpretando a condição S = R = 1 como um comando de inversão. Especificamente, a combinação J = 1, K = 0 é um comando para ativar (set) a saída do flip-flop; a combinação J = 0, K = 1 é um comando para desativar (reset) a saída do flip-flop; e a combinação J = K = 1 é um comando para inverter o flip-flop, trocando o sinal de saída pelo seu complemento. Fazendo J = K o flip-flop J-K se torna um flip-flop Toggle.

Na imagem acima, podemos ver que quando temos J = K = 1, os valores de saída ficam se invertendo, sempre que o sinal de clock é positivo. Ou seja, se Q = 1, no próximo sinal de clock o valor de Q = 0, e vice e versa.

exemplo de uso

Contador Binário

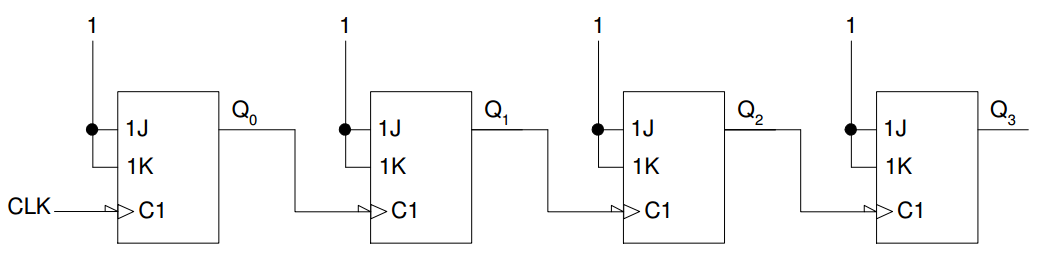

Vamos ver agora um exemplo de uso de Flip-Flops, desenvolvendo um contador binário assíncrono com Flip-Flops JK:

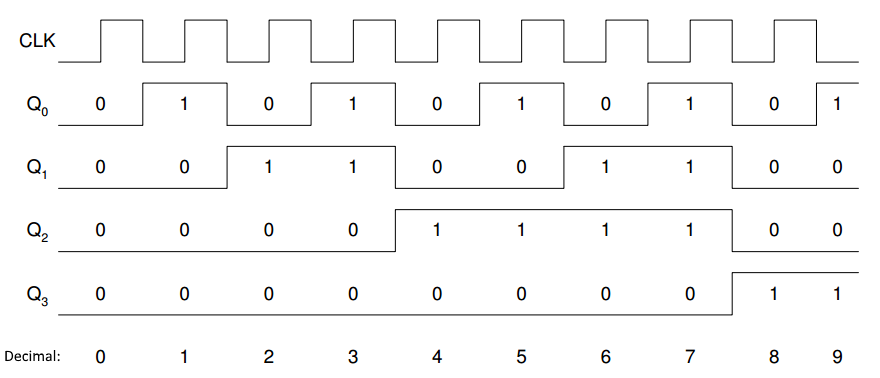

Um contador binário é um registo que, por aplicação sucessiva de impulsos de relógio, segue uma sequência de estados correspondente à numeração binária.

Os contadores por pulsação são extremamente simples de realizar. Os flip-flops não possuem as entradas clock em comum, pois são arranjados de forma que a entrada clock do flip-flop de ordem n seja a saída do flip-flop de ordem n-1. Possui saída binária sequencial e o bit mais significativo da contagem (MSB) está sempre no último flip-flop, considerando como primeiro flip-flop o que recebe os pulsos de clock.

Em outras palavras, este circuito conta os pulsos de entrada e fornece saídas que são a representação binária desta contagem.

Podemos ver melhor na imagem abaixo:

Imagem 1

Imagem 2

Podemos ver na Imagem 1 a implementação de um contator assíncrono de quatro flip-flops JK, ou seja, um contador de quatro dígitos. Podemos perceber também que as entradas J e K estão "setadas" como '1' ou seja, estão em modo toggle, gerando um clock de comprimento de onda maior para o próximo flip-flop, fazendo a contagem binária com alteração correta para cada bit. Vemos também que o clock está "barrado", ou seja, a alteração de estado de cada flip-flop é feita com o clock em nível baixo e não em nível alto como vimos até aqui.

Na imagem 2 podemos ver a saída de cada flip-flop em cada pulso de clock, o binário gerado, onde Q3 representa o bit mais significativo e também o numero decimal (parte de baixo da imagem) correspondente ao binário gerado.

Para que possa entender melhor, veja a animação abaixo de um contador assíncrono de 4 bits em todos os estados possíveis:

Links úteis

Circuitos Lógicos - Manipulando Logisim

Este tutorial foi adaptado do tutorial "Introdução a Flip-Flop" desenvolvido por Matheus Máximo Rodrigues Campos.

Comentários